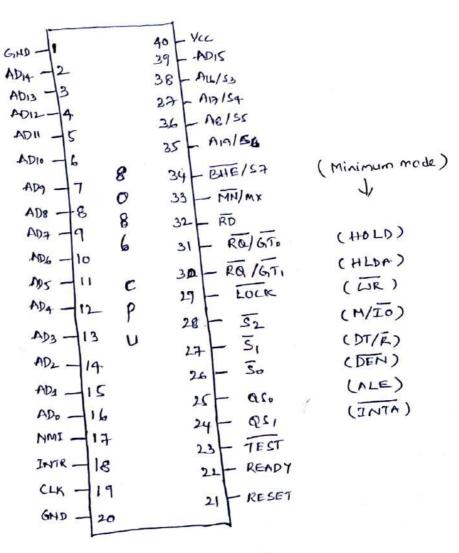

# Pin Configuration of EDEC Hicroprolator:

- -> It is a labit mich processor.

- -> 8086 has a 20-bit address bus can accur upto 20 memory locations (IMB)

- It can support up to 64th 40 ports. - It has multiplexed Address and database Apo-AB-15 and A14-A19.

- -> It requires single phase Clock with 337, dury Cycle to provide Inound timing.

- -> It requires +54 power Supply.

Pin diegram of 8086.

## Signal Description of 8086:-

- -> The 8086 operates in single processor (00) multiprocessor configuration to achieve hish performance.

- -> the 5086 Signals can be Cortesorized in Three Groups. The first are the signal having common functions in minimum as vellas maximum

- -> The second are the signals which have special functions for minimum made and third are the signals having special functions

- -> The following signed descriptions are Common for both modes. ADIS-ADO! These are the time multiplexed memory 3/0 Address and

- Address remains on Be lines during 71 State, while the data in available on the data has during 12,73,

- . Here lines are active high and flect to a tri- state during interrupt acknowledge and local bus hold

A19/56, A18/55, A17/54, A16/53; These are the time multiplexed

- During 71 trese are the most significant address lines for memory operations.

- / During 1/0 operations, Frese lines are low. During memory (61) To operations, status Information is available. on Fox lines for T2, T3, The Twand T4.

- The status of the Interrupt enable flog bit is updated at the beginning of each clock cycle.

- . The S4 and S3 Combinedly indicate which Segment register is presently being used for memory accesses as in below fig.

| 54 | Sa | 2ndication      |

|----|----|-----------------|

| 0  | 0  | Alternate Detar |

| 0  | Ĭ  | Stack           |

| •  | o  | Code            |

| 1  | 1  | Data.           |

| 1  | 8  |                 |

- -> these lines float to tri-state of during the Local Sus hold Aethowledge. The status Line S6 in always low.

- Be address bit one superated from the states bit using Lateres controlled by the ALE Signal.

- the bus high enable is wed to indicate the transfer of data Over the higher order CDIS-D8) Dates bus.

- -> It goes low for the data transfel over DIS-DE and is used to derive chip sclects of odd address memory bank

- -> BHE is low during TI for read, write and interrupt Acknowledge Cycles, Obeneva a syte is to be townsferred on higher byte

- -> Be status Information is available during T2, T3 and T4.

| BHE | A-9<br>0 | whole word upper byte from (or) to even address |

|-----|----------|-------------------------------------------------|

| 0   | 1        | upper byte from (or) to even address            |

| 1   |          | none.                                           |

| 1   | ı        | The the                                         |

RD Read: This Signal on low indicates 150 phecipheral That 15e Processor is perferning memory (x) To read operation.

- READY! This is the Acknowledgement from the stow device (or) merrory that they have completed the data transfer.

- INTR: This is a triggered input. This is sampled during Be Last clock cycles of each instruction to determine the auchientiff of Be request. If Any interrupt request is pending, Be processor enters the Interrupt acknowledge cycle.

- TEST: Bis Exput in Examined by 'WAIT' Instruction. If the TEST pin goes low, execution will continue, else the processor remains in an idle state.

- cit: Be clock Input pravides be basic timing for processor operation and bus control activity.

- MN/MX: Be logic level at This pin decides whether the processor is to operate in either minimum (or) maximum mode.

- # 15e forslowing pin functions are for the minimum made operation of 8086.

Line logically equivalent to S2 in

- H/IO: This is a states line logically equivalent to S2 in maximum mode. when It is low, it indicates the CPU maximum mode. when It is low, and when It is high, is howing an I/o operation, and when It is high, is howing a memory operation. It indicates the CPU is howing a memory operation.

- INTA: This is signal in used as a read strobe for Interrupt acknowledge cycles. i.e. when it goes low, the acknowledge cycles. i.e. when it goes low, the procurer has accepted the Interrupt.

- ALE: This owpur signal indicates the availability of the valid address on the address/deta kness, and us connected to latch enable input of latchers.

- DT/E: this output is used to decide the direction of deer flow through the manspreceives (Bidirectonal Buffers) when the processor sends me dera, This signed in high other the processor is receiving delay, This signaling and when the processor is receiving delay, This signaling and when the processor is receiving delay, This signaling and when the processor is receiving delay, This signaling and when the

DEN: This signal indicates the availability of valid data over the Address / data lines.

It is used to enable the transaccious to separate the data from the multiplexed Address/data signal.

- HOLD, HLDA: When the HOLD Line goes high, it indicates to the processor that another master in requesting the bus access.

- Be processor, after receiving the HOLD request, issued the hold acknowledge signed on HLDA Pin, is the

- . At the Same time, the processor floods the local bus

- If the DMA request is made will the CPU is performing a memory on T/o Cycle, it will see release the local bus during 14 provided.

Be tollowing pin functions are applicable for maximum mode operation of 5086.

52, 51,50 - These are status lines which reflect the type of operation, being carried our by the procussor.

| 152 000011 | 151 00 1 1 00 1 1 | 5000000000 | Indication  Interrupt Actional ledge  Read Ho post  write Halt  Code Access  Read memory  write memory  parsive. |

|------------|-------------------|------------|------------------------------------------------------------------------------------------------------------------|

| •          |                   |            |                                                                                                                  |

LOCK: This output pin indicates that other system bus master will be prevented from gaining the system bus, while the Lock signal is low.

QS1, QS0: Bese lines give Information about Be status of Be Code projetch queue.

| C   |     |                                   |

|-----|-----|-----------------------------------|

| QCI | aso | Indiceron                         |

| 0   | 0   | No operation and ode from 15e     |

| 0   | 1   | First byte of the opcode from the |

| 1   | 0   | emply queur. Syte from Be queue.  |

| 1   | 1   | subsequent byte                   |

Ra/670, Ra/671: These pins ever used by the other local bus master in maximum made, to force the processor to realease the local bus at the end of the processor courser bus cycle. Local bus at the end of the processor courser bus cycle.

- each of the pin is bidirectional with Ra/670 having higher priority than RA/6711.

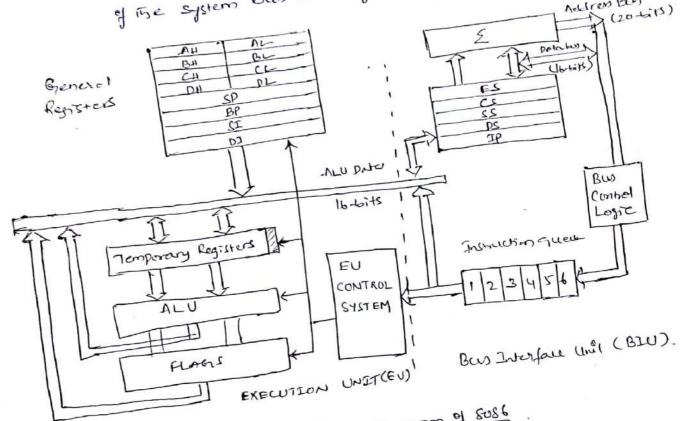

- & BOO BOOK how two blocks BIV and EU.

- . Be BIU performs all bus operations such as Instruction fetching, reading and writing operands for memory and calculating operands. The Instruction the addresses of the memory byten are transferred to the Institution queue.

- · EU executes Instructions from the Instruction System

- Bots units operate Asynchronomy to give the 8086 an everlapping Institution of each and Execution mechanismy which is called as pipelining. This results in efficient whe of the system bus and system performance. Address Ben

# Block Diegram of 8086

## 1. Bus Interface unit:

- 1 It provides a full 16-bit bidirectional data bus and 20-bit address bus.

- Bus Interface unit is responsible for performing all External bus operations.

- Specifically it has functions like Instruction forth, Instruction, qui quelling, operand feeth and storage, Address relocation and Bus control.

- Be BIU uses a mechanisum Known as an Instruction stream queue, This queue permits pre feters of lip to Six syters of Instruction

- Trèse pre fetering Instrutions are held in Il's FIFO queue. with SITS 16-bit data bus, The BIU fetenes two Institution bytes in a single memory cycle.

- Be EV accesses the queen from the output end.

- Be BIU also contains a dedicated added which is Used to generate the so-bit physical address, that is output on the address bus. This address is formed by adding an appended 16-bit Segment address and a 16-bit effect

- 15e BIU is also responsible for generating bus control signals Such as Toole for memory recad (or) carrite and I/o read conwide

## 2. Execution unit:

- the Execution unit is responsible for decoding and executing

- THE EU EXTORUS TRISTRUCTIONS from the top of the queue in the BIU, decodes them, "generates operands if necessary, Prisses Them to be BAU and requests It to perform the read (on write bus (yells to memory (on) I/o and perform the operation specified by the Instruction on the operands

- During Be execution of the Instruction, Be EU Trests Be Steeters and control flags and updates them based on The results of executioning the Instruction.

Transferd Control to a location corresponding to another cert of sequential Instructions, whenever this happens, the BEU automatically resets the queue and Then begins to fetely Instructions from This new location to refin the queue.

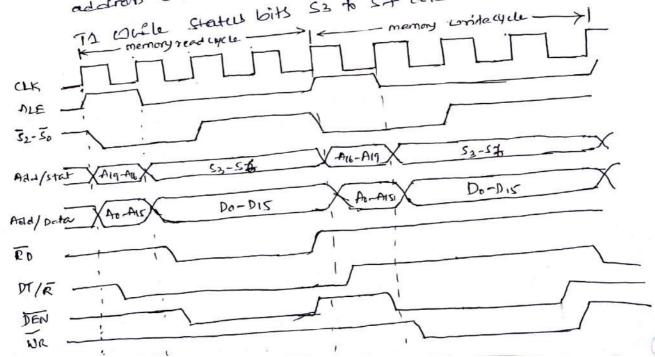

# # General Bus operation of 5086 micro processur?

- referred as a time multiplexed address and data bus.

- Toomreceivers, when ever required.

- repariently, all the processor has cycles consists of at least four clock cycles, these are refused to as T1,72,73,74.

The address in toansmitted by the processor during T1.

The is present on the bus only for one cycle.

- The negative edge of the ALE pulse is used to Separate

The address and the data on that Information. In maximum

The address and the data on that Information. In maximum

The address and the data on that is and see the indicate

The address and the status lines (0, S) and see the used to indicate

The address are the address of the addres

- The status bits (3 to 17 are multiplexed Wits higher order address bits and the BHE signal. Address as Valid during To 15 myh 79

The status bits S3 to 17 are valid during To 15 myh 79

The status bits S3 to 17 are valid during To 15 myh 79

The memory read upon memory write upon to 1

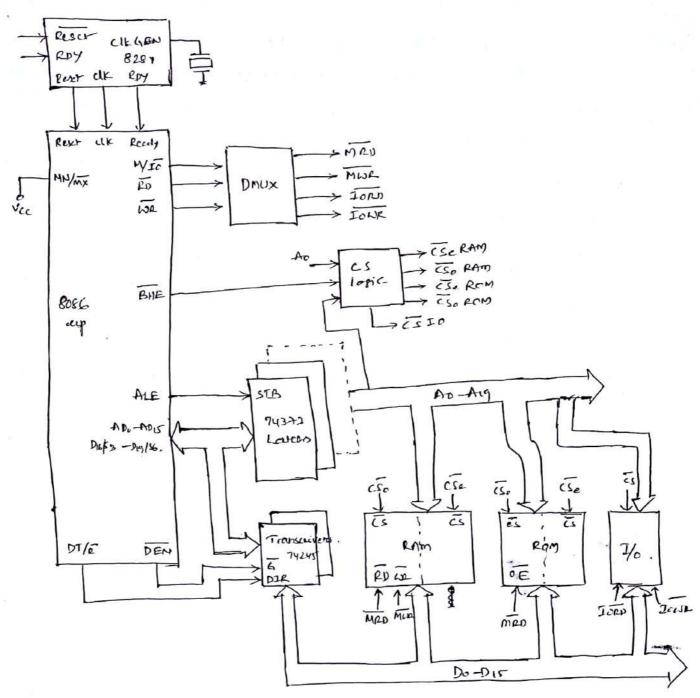

- # Minimum mode operation of soss microprocessor?

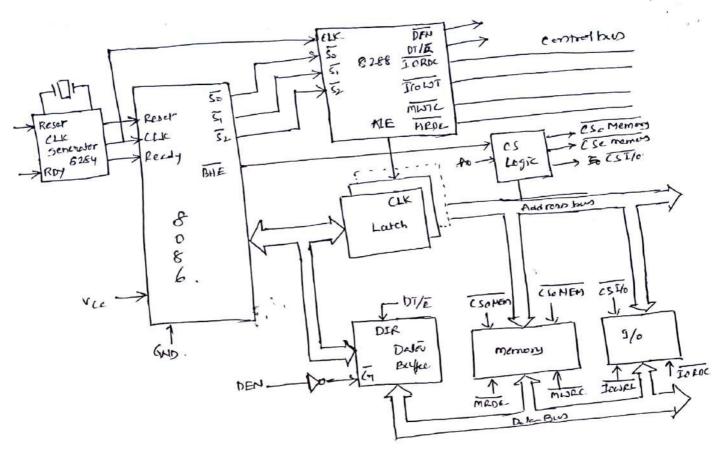

- The microprocessor 8086 is operated in minimum mode by Strapping It's MN/Mx pin to logic 1.

- In This mode, all the control signals are given out by the microprocenor chip Itself. Bere is a single rovicroprocessor in the minimum mode system.

- · The remaining components in the system are Latenes, transreceivers, clock generator, memory, and I/o devices, some type of chip selection logic may be required for selecting memory (or) Ho devices, depending upon the address map

- · hateres are severally suffered output D-type flip-flops libe 14L(373 (or) 8282. Bey are used for Separting Valid address from the multiplexed address/dates signals and are controlled by the ALE Signal generated by 8086.

- v Toansreceivers are the bidirectional Buffers and some times bey are called as dates amplifiers, bey are require to separate the Valid data from the time multiplexed addrovs / data Signals. Bey one controlled by two signals,

- I usually, Eppon are used for nonitor storage, while RAM for weres program storage. A system may contain Todevilles.

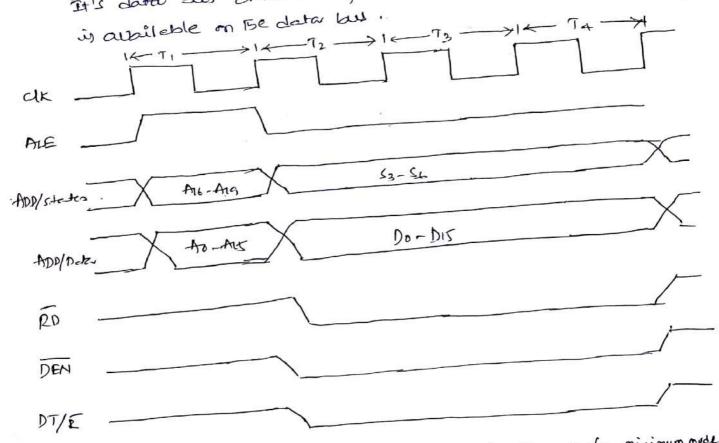

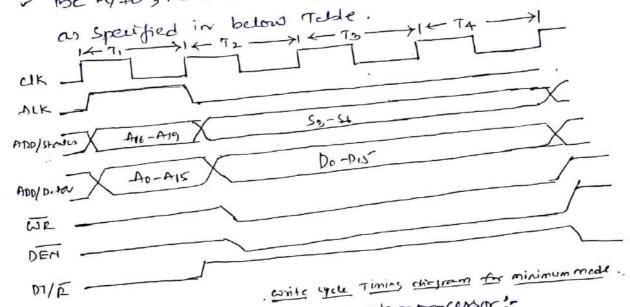

- The working of the minimum mode configuration system can be described in dams of the timing diagrams, the first is the timing diagram for read yell and the second is the timing diegram for write eyele.

HIMINIUM mode 8086 System.

- r Be read eyele begins in 71 will Be assertion of address Latch enable (ALE) Signal and also H/IO Signal. During the negative going edge of this signal, the valid Address is latched on The local bus.

- v The BHE and Ao signals address Low, high (00) both bytes. Form 91 to TA, the M/IO Signal indicates a memory on Ito

- At T2, Be address is removed from the local bus and is sent to be output. be but is then tristand. be read (RD) (ontool Signal in also activated in T2.

- v The read (RD) Signal Calley The address device to enable It's data hus drivers. After RD goes low, The Valid dates

Read Gade Frining diagram for minimum mode

/ Be write eyelle also begins will be assertion of ALE and the emission of the address. The M/IO Signal is again amented to indicate a memory (ur) The operation. In 72. After sending the address in T1, the processor sends the deta to be written to the addressed location.

- We be comes active at the beginning of T2.

- or sytes of memory wor I/o word to be read on write.

- or specified in below Table.

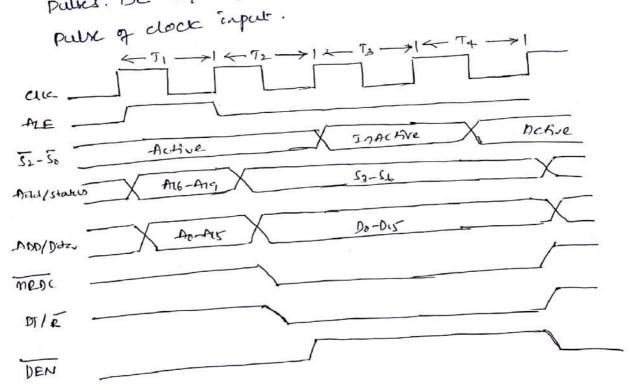

\* Maximum mode operation of sose micro processor:

- In the maximum mode, the 8086 is operated by strapping

- v In This mode, processor drives the status signal \$2,51,50.

another chip called bus controlled drives the control signal wing this status Information.

- In the maximum mode, there may be more than me microprocessor in the system configuration.

- The Bonic function of the bus controller Chip IE8288, it to derive control signals like RD and WR, DEN, DT/R, to derive control signals like RD and WR, DEN, DT/R, ALE see whing the Information by the processor on the states lines.

- risese Inputs to \$258 are driven by CPU.

## Maximum mode 8086 System :

- I orc, IONC and AIONC. BE AEN, IOB and CEN pins are specially weful for multiprocessor Systems.

- If IOB is grounded, It acts as master cascade enable to control cascade \$259A, else It acts as peripheral data enable used in the multiple bus configurations.

- INTA Pin used to issue two Interrupt acknowledge pulses to the Interrupt controlle (or) to an Interrupting device.

- JORC, JONC are Ilo read command and Ilo write command signals respectively. These signals enable an Ilo Interface signals enable and Ilo Interface to read on write the data from loss to the address port.

- write command Signal respectively and may be used as memory read (or) write Signals.

- on send data from (or) to the bus.

- where he only difference between in timing diagram between minimum mode and maximum mode is the status signals used and the available control and advanced command signals.

- \* 20,51,52 are ser at the beginning of bus cycle. 8288 bus controller will output a poure as on the DLE and apply a required signal to It's DT/R pin during T1.

- \* In T2, 8288 will set DEN=1, Tous enabling Transcalulus, and for an Input it will activate MRDC (or) IORC.

Timing for Rellest Signals:

Be request/ Frank response Sequence contains a Series of Force

Pulsed. Be request/ Frank pins one checked at each mising

Memory Read Timing in maximum mode.

## Internal Registers of 5086 microprocursor:

- The 8086 has four groups of the wer accessible Internal Registers. Bey are Be Instruction pointer, forur data registers, four pointers and index registers, four segment registers.

- ~ 8086 has a total of fourteen lb-bit registers, including a 16-bit register called the status register. (ii) flag register.

- · Dere are four different 64KB Segments for Instructions, Stack, data and Extra data.

code segment (Cs):- is a 16-bit register containing address of 64KB Segment Wills processor Instructions. The processor was Cs segment for all accerses to Instructions rejevenced by Instruction pointer (IP) registel.

Stack Segment (SS):- is a 16-bit register Containing address of 64kB Segment Wits program stack. By default, the Processor Assumes that all deta rejevenced by the stack printer (Sp) and base pointer (BP) register is located in lea

Data segment (DS): - is a 16-bit register containing address of 64kB Segment Wils program dela. By default, the processor Assumes that all dates referenced by general registers (AX,BX, CX, DX) and index registe (II, DI) is located in the data

Accumulator: - register consisto of two 8-bit registers ALGAH, which can be combined together and used as a lb-bit reporter AX. Accumulator can be used for Ito operations and String

Box orgiter: - consists of two 8-bit orgisters BL and BH, Which can be combined together and used as a 16-bit registee BX. & It is wouldy contains a detail pointer used for board, based indeped (or) registee in direct Addressing.

Addressing Modes: - Addressing mode refers to the mechanism by Which the operands are Specified for an operation. Depending on the type of operands used, there are I addressing modes available.

1. Immediate mode: - In this mode, Be Instruction contains full (on) liberit Immediate data along will be manemonic. Data (on be moved to 8-bit on 16-bit register, or memory likerian wing the address (or) register.

Ep: MOV Ax, 1234 H MOV [2000H], 25 AND AL, 3FH.

2. Regisse mode? In This mode, the operands are available in general purpose registers. Instruction Specifies the Register Name.

Ex: MOV CL, DL

ADD BL, AL

XOR CX, DX.

3. Direct mode: Here, Be Instruction contains 16-bit GASU-CEffective Address) EA of the memory Location.

Segment register, and then the operand will be fetered from memory.

PA = EA + (DS \* 10)

Ep: MOV BL, NUM

MOV [3455 H], AL.

4. Indirect model: 8086 provides many "Indirect addressing modes" (where one operand is in memory) which are extensively used in programming.

a Register indirect mode: In This mode, the Instruction Contains, a 16-bit register name which contains the EA. Wring This EA, PA is calculated. Defocult segment register for memory is Ds.

EX: MOV AL, BYTE MR[BX].

AND CX, WORD PTR[BX].

b. Register relative mode (or) indexed mode: In this mode, Be Instruction contains a labor name (which contains an address) and a signed displacement. Adding the register contents will displacement gives the EA.

PA = EA + (DS \* 10 H)

EA = (BX) { 8 - bit displacement (Sign - Extended)}

(Or)

(SI)

(DI)

(DI)

Ex's MOV AL, BYTE PTR 50 [BX]

DEC WORD PTR [DI+30].

Count register: - constats of two B-bit registers CL and CH, which Can be combined together and used as a 16-bit register CX. count register can be used in loop, shift/rotate Instructions and as a counter in string manipulation.

Douba register: - consists of two 8-bit registers DL and DH, Which can be combined together and used as a lb-bit tagittee DX. Data régisse can be used as a port number in I/o operations In Integer 32-sit multiply and divide Instructions the DX register contains high-order word of the resulting number.

\* the following registers are both general and index registers: Stack pointu (Sp) is a 16-sit regrester pointing to program stack Base pointer (Bp): is a la-bit register pointing to data in stack segment. Be registed in usually used for based, based indexed (or) register indirect addressing.

Source index (SI): - is a 16-bit register, SI is used for indexed, based indexed, and register indirect addressing as well as a source data address in string manipulation

Destination index (DI): - is a labilit register. DI is used for indexed, based indexed and registee indirect aderessing, as well as a destination data address in String manipulating Instructions.

Instruction pointer (IP) in a 16-bit register:

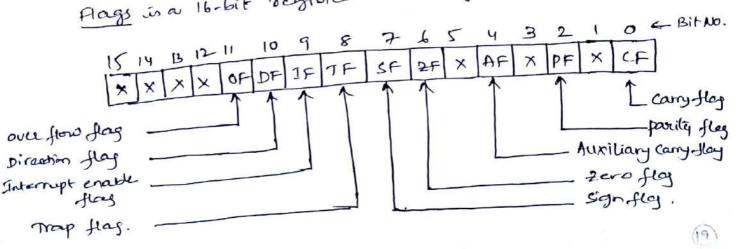

Flags is a 16-bit regictee Containing 9 one bit flags.

Overford flag (of): - Set If 15e result is too long positive.

number, or is too Small negative number to fit into destination operand.

Direction flag (DF): - If set then string manipulation instructions will auto-decrement index registers. If cleared then the index registers. If cleared then the index registers will be auto-incremented.

Interrupt emble flag (IF)! - Setting This bit enables maskable

Interrupts.

Single-step florg (TF)! - If set then single-step interruption, will occur after the next Instruction,

Sign Flag (SF); - Set If the most significant bit of the result is set.

zero flag (2+): - Set If The result in Jero.

Auxiliary Carry Play (AC)! - Set If There was a carry from (or) borrow to bits 0-3 in the AL register.

partily Flag (PF): - Set If partily (15e number of "1" bits) in the low-byte of the result is even.

carry Flag (CF): - Set if Bere was a Carry from (or) borrow to the most significant bit during Law result.

#### 80286 Microprocessor:

There are two operating modes for 80286.

- > The real address mode and protected virtual address mode. As explained in the real address mode the processor can address up to 1MB of the physical memory.

- The virtual address mode is for multiuser and multitasking system. In this mode of operation the memory management unit can manage up to 1 GB of the virtual memory though the real memory may be much less, only 16 MB.

- ➤ Basically in this mode one user do not interfere with the other. Also users cannot interfere with the operating system. These features are called protection.

The 80286 contains four processing units:

- 1. Bus unit

- 2. Instruction unit

- 3. Execution unit

- 4. Address unit

- ➤ All memory and I/O read /write operations are performed by BU. While the current instruction is being executed, the BU pre fetches instructions and keeps them in a queue of six bytes.

- The function of IU is to decode the perfected instructions and to maintain a queue of 3 decoded instructions for execution. The EU executes instruction.

- > The address unit computes address of memory or I/O devices, which is to be sent by BU for read and write operation. All the four units work in parallel within the CPU.

- > This type of parallel operation is called pipelining. All modern 16-bit CPU use pipelining. In pipelining several execution units in a processor work simultaneously in parallel.

#### 80386 Microprocessor:

- The Intel 80386 (also called Intel386) is a microprocessor which has been used as the CPU of many personal computers since 1986. The 80386 operated at 5 million instructions per second to 11.4MIPS for the 33MHz model.

- This is a 32 bit microprocessor it has a circuitry of 275000 transistors. It was basically introduced in the year 1985. It is compatible with 8086, 8088, 80186, 80286 microprocessors.

- ➤ It also contains a four-level protection mechanism on the chip itself. It has a total of 129 instructions. The 80386 is a 32 bit microprocessor with a non multiplexed 32 bit address bus housed in a 132 pin grid array package.

- ➤ Basically this microprocessor has three versions: 80386SX, SL and DX. The DX version has a 32 bit internal architecture and a 32 bit data bus whereas the SX and the SL version have a 32 bit internal architecture but a 16 bit wide data bus.

- These versions operate from 20MHz to 33MHz. It is capable of addressing 4G bytes of physical memory and through its memory management unit it can address 64 terabytes of the virtual memory.

- The processor can operate in two modes: Real and protected. In the real mode physical address space is 1Mbytes (20 address lines), which is extended to 4G bytes in the protected mode (32 address lines). The primary difference between these modes is the availability of the memory space and the addressing scheme.

- The 80386 has 32 bit registers and is upward software compatible with the 8086. The execution of the instructions is highly pipelined and the processor is designed to operate in a multiuser and multitasking environment. It has the protection mechanism for this type of environment.

- ➤ It has basically six functional units: bus interface unit, code pre fetch unit, instruction decode unit, execution unit, segmentation unit and the paging unit. It has the provision for both memory segmentation and paging. A page is of fixed size 4KB each. Segment vary in size, 4GB is the maximum size of a segment.

- ➤ The 80386 has 11 addressing modes: register, immediate, direct, register indirect, based, indexed, scale indexed, base indexed, base scale indexed with displacement and base scale indexed with displacement addressing. In the scale indexed addressing the contents of an indexed register are multiplied with a scaling factor and the result is added to the displacement to obtain the operand's offset.

- As explained earlier it has 32 bit register and has eight general purpose registers, six 16 bit segment registers, also has a 32 bit instruction pointer, six debug registers and a 32 bit status register. The 80386 has a segment descriptor register associated with each segment register. The 80386 was widely used in powerful PCs before the 80486 was developed.

### 80486 Microprocessor:

- Basically this is an upgraded advanced version of 80386 and it was released in the year 1989.

- ➤ It contains a 32 bit CPU, a floating-point math coprocessor, unified instruction and data cache memory and memory management unit in a single IC.

- ➤ It contains an electronic circuitry of 1.2 million transistors. Its operating frequency for its different versions is 25, 33, 66 and 100MHz. It is 3 to 5 times faster than 80386.

- ➤ Basically this is available in two versions: DX and SX. The DX type version is a 32 bit processor housed in a 168 pin grid array package and can operate with the clock frequencies from 25 to 66 MHz as explained earlier. The important additional features of the 486 processor in comparison with the 386 processor are as follows.

#### The 486 processor includes:

- ➤ Built in math coprocessor. In the 386 system, a math coprocessor is an external device. Therefore, the math instructions in 486 systems are executed three times faster than in 386 systems.

- > 8K byte of code and data cache memory on the chip.

- ➤ Highly pipelined execution unit. Therefore the execution time for many instructions is one clock period. Basically we do not use 80486 but instead of that we usei486 because of a court ruling that prohibited trade marking numbers. Intel dropped number-based naming altogether with the successor to the i486-thePentium processor. The 486 contains the following functional units:

- > Execution unit

- ➤ Control unit

- > Bus interface unit

- > Code pre fetch unit

- > Instruction decode unit

- > Segmentation unit

- > Paging unit

- > Cache unit

- Floating point unit.

- The code pre fetch unit contains a 32 byte queue to store fetched instruction codes. The control unit also contains a control ROM to store micro codes. The segmentation unit calculates linear address (the starting address of the segment plus the offset) from the logical address. The address given in the program is called the logical address.

- ➤ It also provides 4-level of protection for isolating and protecting tasks and the operating system from each other. The paging unit provides the paging facility within a segment. It translates the linear address into the physical address. The actual capacity of RAM and ROM existing in a computer is known as physical memory.

- ➤ The segmentation and the paging unit constitute memory management unit. In summary, the 486 is a high speed, high performance 32bit microprocessor. It executes many of its instructions in one clock cycle by using highly pipelined execution units.

- ➤ It is designed to facilitate the execution of high level languages and suited for multiprocessing and multitasking systems. In the early 1990s, 486 was generally used in high end microcomputers and network environments

### # Assemble Directive :-

the word defined in This section are directions to the assemble, the assembled directives described here are those for the Intel 8086 macro assendu (ASM86).

ASSUME: - BE ASSUME directive is used to tell the assemble the name of the logical sigment it should use for a specified segment. ASSUME CS: CODE, For Example, tells The aventure that the instructions tora program are in a topical segment named CoDE.

DB-DEFINE BYTE: - Be DB directive is used to declare the Syle-type Vortiable, (08) to set aside one (or) more storage locations of type byte in memory.

CLERRENT\_TEMPERATURE DB 42H, the Statement

for Example, tell the assemble to reserve 1 byte of memory for a variable nambed current\_TEMPERATURE and to put the volue 42H intoar memory location When the program is loaded into RAM

DT-DEFINE TEN BYTES: - DT is used to tell the assembles to define a variable which is 10 bytes in length (en) to reserve 10 bytes of storage in

Be Statement PACKED-BCD DT 11223344556677889900 Will declare an arry named PACKED-BCD which is lo byter in length. It will initialize loc lobytes him the values 11223344556677889900 When Be program a loaded into memory to be sun.

ENDP-END PROCEDURE: - This directive is used along vills the name of the procedure to indicate the end of the procedure to the Assemble.

Ex'- Square - ROOT PROC : Start of procedure

: procedure instruction

: statement

SQUARE\_ROOT ENDP : End of procedure.

$\cup$

ENDS - END SEGMENT: This directive in used with the name of a sympa" to indicate the end of their degical segment.

ENDS in used with the segment directive to "bracker" a logical sympar containing instructions on data.

Ex: CODE SEGMENT: Start the logical segment contains code

: Instruction Statements.

CODE ENDS: End of Segment named CODE.

EQU - EQUATE: - EQU is used to give a name to some Volucius Symbol.

Each time be assemble finds be given name in the program, it

will replace be name with the value (or) Symbol you equate that

name.

Ex: CORRECTION-FACTOR EQUIDAN LA 150 Start of 150 your program.

and later in the program you write the Instruction Statement

ADD AL, CORRECTION-FRATOR. (HILL INLIGHT INL).

EVEN\_ALIGN ON EVEN MEMORY ADDRESS'- BY EVEN directive leus Be axemble to increment Be location counter to Beneal even address.

INCLUDE - INCLUDE SOURCE CODE FROM PILE: - This directive is used to tell the assemble to insert a block of source Code from the named file into the current source module.

OFFSET: OFFSET is an operator which tells The assemble to derermine the offset can displacement of a named data item (as procedure from the store of the segment which contains It.

MOV BX, OFFSET PRICES, for EXO IT HILL determine The offset of the variable prices from the start of the segment in which prices is defined.

ORG-ORIGINATE; - 150 ORG directive allows you to set 150 location counter to a desired value at any point in 150 program.

ORG 2000H 1005 The assembles to set the location counter to 2000H.

IF-THEN program: - 15e IF-THEN Structure has 15e format

IF condition THEN action

ausm.

This structure says that If the stated condition is found to be true, the series of autims following THEN Will be executed. If the condition is false, execution will skip over the actions after the THEN and proced with the next mainline Instruction.

CMP Ax, BX; compare EP.

JE THERE ; If equal Ben skip correction

ADD Ax,0002H; add correction factor

THERE; MOV Ch, OTH ; load count.

IF-THEN-ELLE program: Be IF-THEN-ELSE Structure is used to indicate a choice between two attornative courses of Action.

> IF condition THEN action

ELSE

aution.

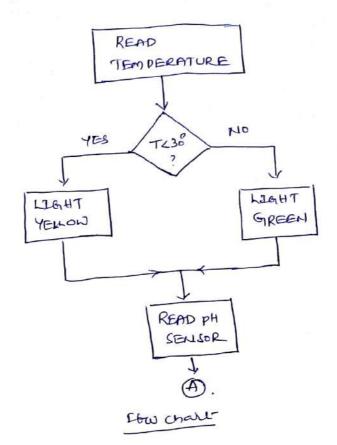

While making PCB (printed Circuit board), part of the Job of This 886 is to cheek a & temperature of the solution and turn on a scen lamp loss a yellow lamp depending upon the value of the temperature it reads in.

If the temperature is below 30°C, we want to turn on a Yellow lamp to tell the operator that the solution is not up to temperature If the Temperature is greater than con equal to 30°C, we want to higher a green lamp.

We can represent the algorithm for This problem in two ways as

READ TEMPERATURE

TEMPERATURE 238 THEN

LIGHT YELLOW LAMP

ELSE

LIGHT GREEN LAMP.

READ PH SENSOR

PSEULO CODE

### Programe,

ASSUME CS: CODE

MOV DX, FFFEH

MOV AL, 99H

OUT DX, AL

MOU DX, FFF8 H

IN AL, DX

CMP AL, 30

IMP JB YELLOW

JMP GREEN

YELLOW' MOV AL, OIH

MOY DX, FFFAH

OUT DX, AL

Jup EXIT

GREEN, MOU AL, OZH

MOL DX, FFFAH

OUT DX AL

's point Dx to port control Reporter

; Load Control word to Initialize ports.

; Send control word to port control registers.

; point Dx at input port.

; Read Temp from Scher on Input port

; compare Temp W15 30°C.

; IF Temp <30' THEN higher Yellow lamp

I ELSE Light GREEN lamp.

; load code to light yellow lamp

; point Do at output post

; send code to light yellow lamp

; Goto next mainline Instructing

P. T. O.

(27)

GREEN: MOV AL, 02H

; Load code to light green lamp.

MOV DX, FFFAH ', point DX at output port

OUT DX, AL

; send code to light occan lamp.

EXIT : MOV DX, FFFEH

; next mainline anstruction

IN AL, DX

; Read ph sensor.

CODE ENDS END

WHILE -DO programs- WHILE -DO Structure has the form. #

LIHELE Some Condition is present Do action action.

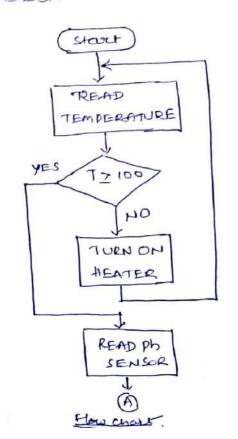

In controlling a chemical process, we want to bring the Temperature of a solution up to loo'c before going on to the next step in the

If the Solution temperature is below 100°C, we want to turn on a heater and Dait for the Temperature to reach 100°.

The WHILE-DO Structure fits This problem because we want to Check the condition (temperature) before we turn on the heater.

READ TEMPERATURE WHILE TEMPERATURE < 100°C DO TURN HEATER ON TURN HEATER OFF

Pusedo Code

MOV DX, FFFEH

is point Dx to port control register

MON AL, 37H

; control word to set up output post

OUT DY, AL

; Send Control word to port

TEMP\_IN; MOV DX, FFFEH

; point at input port

IN AL, DX

; Input Temperature dasa

CMP AL, 100

; If Temp 2 100 15en

JAE HEATER-OFF ; two heard off.

MOV AL, BOH

; else load code for heater on

MOV DO, FFFAH

? point Dx to output port.

OUT DX, AL

; tuen heater ON

JMP TEMP-IN

; LIHTLE tempc 100 read temp again

HEMER-OFF : MOV AL, OD

" Load Code for beatch off.

MOV DN, FEFAH

; point Dx to output port

OUT DX, AL

; tuen heater OFF

CODE ENDS

END .

REPEAT - UNTIL PROGRAMS: - REPEAT \_ UNTIL STRUCTURE has The form

REPEAT

action

UNTIL some Condition is present.

This structure is that, the acrim (m) series of actions is done mue before the Condition is Cheeted.

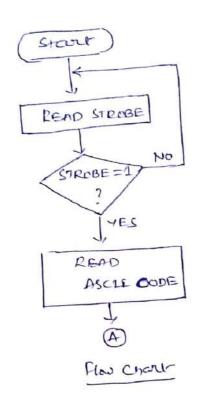

If we want to seed The data from Keyboard, 10 and road valid data, we have to look at the Stroke Signed and Text it over and Over until It goes high.

Implementation of the algoriton with Accordy language for REPEAT\_UNTIL

REPEAT

READ KEY PRESSED STROBE

UNITL STOROBE = 1

READ ASCIT CODE FOR KEY PRESSED

Psecudo Code

Programo-

ASSUME CS: CODE

MOV DX, FFFAH

LOOK-AGAEN; IN AL, DX

AND AL, OI

JZ LOOK - AGAIN

MOV DX, FFFE H

IN AL, DX

: point DX ex stooks port

; Read keyband strobe

Mark extra bits q &r Flags.

if stroke is low teen keep looking

; else point DX at data post

; Read in ASCIE Code

CODE ENDS

END .

#### Macros

- Macros are just like procedures, but not really. Macros look like procedures, but they exist only until your code is compiled, after compilation all macros are replaced with real instructions.

- If you declared a macro and never used it in your code, compiler will simply

ignore it. Emu8086.inc is a good example of how macros can be used; this file

contains several macros to make coding easier for you.

-xx-

#### INSTRUCTION TYPES

The 8051 instructions are divided among five functional groups:

- 1. Arithmetic

- 2. Logical

- 3. Data transfer

- 4. Boolean variable

- 5. Program branching

#### 1. Arithmetic Instructions

With the arithmetic instructions four addressing modes may be used. These modes are direct, indirect, register and immediate. For instance the add-with-carry instruction ADDC A, operand2 has the following four forms:

| Instruction |           | Operation                                    | Comments                                                                         |  |

|-------------|-----------|----------------------------------------------|----------------------------------------------------------------------------------|--|

| ADDC        | A. Kn     | Add register to accumulator with carry       | Rn = register R0 to R7 from currently selected register bank.                    |  |

| ADDC        | A, direct | Add direct byte to accumulater with carry    | Direct = 8-bit internal data's location address.                                 |  |

| ADDC        | A, @Ri    | Addirect RAM to accumulator with carry       | @Ri = 8-bit internal data RAM location<br>addressed indirectly through R0 o: R1. |  |

| ADDC        | A, #data  | Add immediate data to accumulator with carry | #data = 3-bit constant included in the instruction.                              |  |

Most of the arithmetic instructions execute in twelve oscillator clock periods with the following three exceptions:

| Instruc    | ction      | Operation              | Oscillator periods |  |

|------------|------------|------------------------|--------------------|--|

| INC<br>MUL | DPTR<br>AB | Increment data pointer | 24                 |  |

| DLZ.       | AB         | Multiply A and B       | 48                 |  |

| DI         | AD         | Divide A by B          | 48                 |  |

#### 2. Logical Instructions

The logical instructions can perform Boolean operations on the data contained either in the accumulator or in an internal RAM location. Those logical instructions that use the accumulator as one of the operands have the same addressing modes as those found in arithmetic instruction. Examples of such instructions are:

| Instruction |           | Operation                        | Comments                                                                      |  |

|-------------|-----------|----------------------------------|-------------------------------------------------------------------------------|--|

| ORL         | A. Rn     | OR register to accumulator       | Rn = register R0 to R7 from currently selected register bank.                 |  |

| ORL         | A. direct | OR direct byte to accumulator    | Direct = 8-bit internal data's location address.                              |  |

| ORL         | A, @Ri    | OR indirect RAM to accumulator   | @Ri = 8-bit internal data RAM location addressed indirectly through R0 or R1. |  |

| ORL         | A, #data  | OR immediate data to accumulator | #data = 8-bit constant included in the instruction.                           |  |

Note that in addition to the **ORL A, direct** instruction we also have the equivalent "mirror" instruction **ORL direct, A** (OR the accumulator to the direct byte). All such instructions execute in twelve oscillator clock periods. Apart from the logical instructions that use the accumulator as one of the operands, there are three logical instructions that perform Boolean operations directly on any byte in the internal data memory without going through the accumulator. The table below gives a summary of these instructions.

| Instru | ction         | Operation                                  | Comments              |  |

|--------|---------------|--------------------------------------------|-----------------------|--|

| ANL    | direct, #data | AND immediate data to direct byte          | Example: ANL P2.#0FFH |  |

| OKL    | direct, ∓data | Or immediate data to direct byte           | Example: ORL P2,#0FFH |  |

| XRL    | direct, #data | Exclusive OR immediate data to direct byte | Example: XRL P2,#0FFH |  |

These three instructions take 24-oscillator clock period to execute. Note that these instructions perform what is known as "read-modify-write" operation. In a "read-modify-write" instruction the datum in the direct address location is first

read, then the logical operation is performed on the read datum with the immediate byte, and

Finally the result of the logical operation is written back to the direct address location.

The logical group of instructions also contains four rotate instructions, which operate on the contents of the accumulator, and a swap instruction (SWAP A). The swap instruction is useful in BCD arithmetic manipulations.

#### 3. Data Transfer Instructions

This group contains the largest number of instructions that enable us to move data within the internal RAM, move data between the internal RAM and external RAM, and three instructions that allow us to manipulate look-up tables. The following table contains some examples of data transfer instructions. Note that the stack in the 8051 is implemented in the on-chip RAM. Unlike the stack implementations in other microprocessors the stack grows "upwards" in memory, i.e. towards higher memory addresses. The execution of the PUSH instruction first increments the stack pointer, and then copies the indicated byte into the stack.

| Instruction       | Operation                                | Comments                                                                                         |

|-------------------|------------------------------------------|--------------------------------------------------------------------------------------------------|

| MOV A. Rn         | Move register to accumulator             | Register addressing.                                                                             |

| MOV direct, A     | Move accumulator to direct byte          | Direct addressing.                                                                               |

| MOV Rn. =data     | Move immediate data to register          | Immediate addressing.                                                                            |

| MOV @Ri, A        | Move accumulator to indirect RAM         | Indirect addressing. Move to internal RAM.                                                       |

| MOV direct, @ Ri  | Move from indirect RAM to direct byte    | Indirect addressing. Move from external RAM to internal RAM.                                     |

| MOV DPTR, #datal6 | Load data pointer with a 16-bit constant | Immediate address.                                                                               |

| MOVX @DPTR, A     | Move accumulator to external RAM         | Indirect addressing.                                                                             |

| MOVC A. @A+PC     | Move Code byte relative to PC to ACC     | Index addressing.                                                                                |

| PUSH direct       | Push direct byte into stack              | Direct addressing. Stack itself is accessed using indirect addressing through the stack pointer. |

| XCH A. @Ri        | Exchange indirect RAM with accumulator   | Indirect addressing                                                                              |

#### 4. Boolean Instructions

The 8051 has a range of Boolean variable manipulating instructions which enable us to set or reset individual bits within some of the locations in the internal RAM, and some of the special function registers. We give some examples of these instructions in the table below.

| Instruction | Operation                             | Oscillator period |

|-------------|---------------------------------------|-------------------|

| CLR C       | Clear Carry bit                       | 12                |

| CLR bit     | Clear direct bit                      | 12                |

| SETB C      | Set Carry                             | 12                |

| CPL bit     | Complement direct bit                 | 12                |

| ANL C, bit  | AND complement of direct bit to Carry | 24                |

| ORL C, bit  | OR direct bit to Carry                | 24                |

| MOV bit, C  | Move Carry to direct bit              | 24                |

### 5. Program branching Instructions

This group contains conditional and unconditional branch instructions. Some of the conditional branch instructions which test individual bits such as JC *rel* (jump if Carry is set) are found in the previous instruction group. The following is a list of some of the program branch instructions.

| Instruction          | Operation                                                | Comments                                                |

|----------------------|----------------------------------------------------------|---------------------------------------------------------|

| ACALL addr11         | Absolute subroutine call                                 | Absolute addressing                                     |

| LCALL addr16         | Long subroutine call                                     | Long addressing. Call to subroutine in external memory. |

| RETI                 | Return from interrupt                                    |                                                         |

| SJMP rel             | Short jump                                               | Relative addressing.                                    |

| JMP                  | Jump indirect relative to the data pointer               | Indexed addressing.                                     |

| CJNE A, #data,rel    | Compare the immediate data to the                        | Compare – immediate                                     |

|                      | accumulator and jump if not equal                        | Jump – relative                                         |

| CJNE @Ri. ≠ data,rel | Compare immediate data to indirect and jump if not equal | As above                                                |

| DJNZ Rn, rel         | Decrement register and jump if not zero                  | Register and relative addressing.                       |

| DJNZ direct, rel     | Decrement the direct byte and jump if not Zero           | As above                                                |

| JNC rel              | Jump if Carry is not set                                 | Jump – relative addressing                              |

| JBC bit. rel         | Jump if direct bit is set and clear bit                  | As above                                                |

#### ADDRESSING MODES

In short, a way to addressing a operand is nothing but addressing mode. Operand means data on which we are going to operate i.e source data. We can address the operand using direct address or by using register or we can address the data using some numerical value etc.

#### MOVA,#6BH

In this example 6BH is operand i.e. source data. After execution of this instruction 6BH is added to the accumulator.

We can execute this instruction by using 5 different ways i.e we can use 5 different addressing modes to execute this instruction. Following are the different type of addressing modes.

- Immediate addressing mode

- · Direct addressing mode

- Register addressing mode

- Register indirect addressing mode

- Indexed addressing mode.

#### 1. Immediate addressing mode:

As word indicates 'immediate' this addressing mode transfers 8 bit immediate data to destination.

#### MOVA,#6BH

This instruction moves immediate data hex 6B to accumulator.

#### 2. Direct addressing mode:

This is type of addressing mode in which the address of the data (source data) is given as operand..i.e. it is given directly in the form of numerical data.

#### MOVB,20H

The instruction above moves value at address 20H memory location to register  ${\sf B}$  .

Here 20H is address of SFR.

The difference between direct addressing and immediate addressing mode is, we don't use '#' in direct addressing mode, unlike immediate mode.

#### 3. Register addressing mode:

This is type of addressing mode in which we use the register name directly as source data.

MOV A, R5

After execution of this instruction content of register R5 is get copied to location accumulator.

4. Register direct addressing mode:

In this mode of addressing address of source data is given by value at register indirectly that's why we call it as a indirect register addressing mode.

e.g. MOV A, @R1

Here in this instruction register R1 holds the address, suppose value at R1 is '20H' then after execution of above instruction value at location 20H is transferred to to accumulator.

Here symbol '@' indicates address. In this type addressing mode we can use only register R0 and R1 to provide indirect address.

Indexed addressing mode:

In this type of addressing mode we use following instruction:

1. MOVC A, @A+DPTR and 2. MOVC A, @A+PC 'MOVC A, @A+DPTR' instruction copies value at the location given by result of

addition of content of accumulator and 16 bit register DPTR. Suppose Accumulator contain '01H' and DPTR contains value '1000H' then after the execution of instruction 'MOVC A, @A+DPTR the value at address '1001H' will be transferred to accumulator.

'MOVC A, @A+PC' instruction copies value at the location given by result of addition of content of accumulator and 16 bit register PC (Program counter). Suppose Accumulator contain '01H' and PC contains value '1000H' then after the execution of instruction 'MOVC A, @A+DPTR the value at address '1001H' will be transferred to accumulator.

#### ASSEMBLY LANGUAGE PROGRAMMING

Simple addition is done within the 8051 based on 8 bit numbers, but it is often required to add 16 bit numbers, or 24 bit numbers etc. This leads to the use of multiple byte (multi-precision) arithmetic. The least significant bytes are first added, and if a carry results, this carry is carried over in the addition of the next significant byte etc. This addition process is done at 8-bit precision steps to achieve multiprecision arithmetic. The ADDC instruction is used to include the carry bit in the addition process. Example instructions using ADDC are:

ADDC A, #55h ; Add contents of A, the number 55h, the carry bit; and put the sum in A

ADDC A, R4; Add the contents of A, the register R4, the carry bit; and put the sum in A.

Subtraction Computer subtraction can be achieved using 2's complement arithmetic. Most computers also provide instructions to directly subtract signed or unsigned numbers. The accumulator, register A, will contain the result (difference) of the subtraction operation. The C (carry) flag is treated as a borrow flag, which is always subtracted from the minuend during a subtraction operation. Some examples of subtraction instructions are:

SUBB A, #55d ; Subtract the number 55 (decimal) and the C flag from A; and put the result

in A.

SUBB A, R6 ; Subtract R6 the C flag from A; and put the result in A.

SUBB A, 58h ; Subtract the number in RAM location 58h and the C flag From A; and put the

result in A.

Increment/Decrement The increment (INC) instruction has the effect of simply adding a binary 1 to a number while a decrement (DEC) instruction has the effect of subtracting a binary 1 from a number. The increment and decrement instructions can use the addressing modes: direct, indirect and register. The flags C, AC, and OV are not affected by the increment or decrement instructions. If a value of FFh is increment it overflows to 00h. If a value of 00h is decrement it underflows to FFh. The DPTR can overflow from FFFFh to 0000h. The DPTR register cannot be decremented using a DEC instruction (unfortunately!). Some example INC and DEC instructions are as follows:

INC R7; Increment register R7

INC A; Increment A INC @R1; Increment the number which is the content of the address in R1

DEC A; Decrement register A

DEC 43h; Decrement the number in RAM address 43h

INC DPTR; Increment the DPTR register

#### Multiply / Divide

The 8051 supports 8-bit multiplication and division. This is low precision (8 bit) arithmetic but is useful for many simple control applications. The arithmetic is relatively fast since multiplication and division are implemented as single instructions. If better precision, or indeed, if floating point arithmetic is required then special software routines need to be written. For the MUL or DIV instructions the A and B registers must be used and only unsigned numbers are supported.

### Multiplication

The MUL instruction is used as follows (note absence of a comma between the A and B operands):

MUL AB; Multiply A by B. The resulting product resides in registers A and B, the low-order byte is in A and the high order byte is in B.

#### Division

The DIV instruction is used as follows:

DIV AB; A is divided by B. The remainder is put in register B and the integer part of the quotient is put in register A.

# Decimal Adjust (Special)

The 8051 performs all arithmetic in binary numbers (i.e. it does not support BCD arithmetic). If two BCD numbers are added then the result can be adjusted by using the DA, decimal adjust, instruction:

DA A; Decimal adjust A following the addition of two BCD numbers.

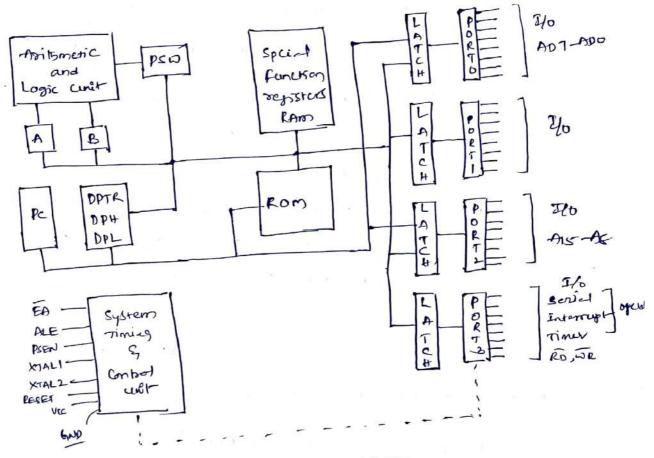

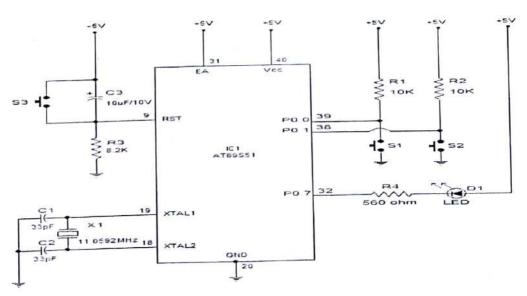

- # Architecture of SorI micro controller:

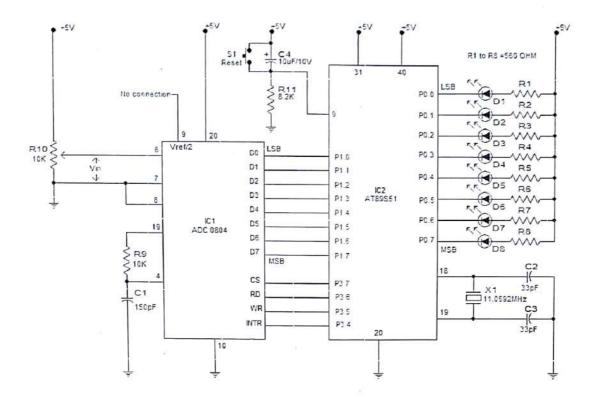

- → 8051 MEro Controller is The 8-bit micro Controller.

- > 54 power supply is required to operate, It is a 40 pic Il.

- > It works with a clock of prency of 11.05962 MHJ.

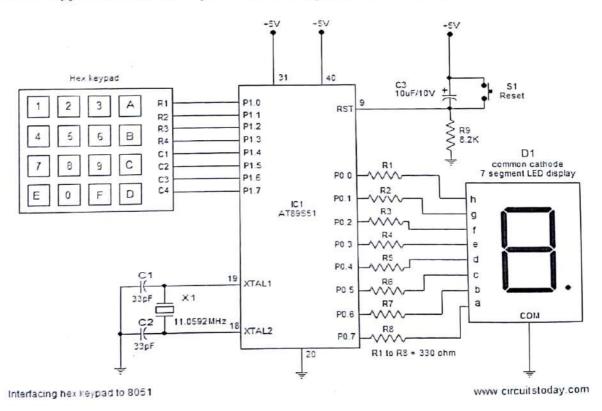

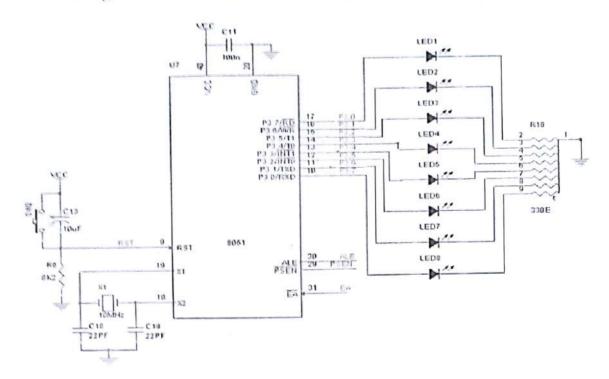

Fig. Architecture of Micro Controller 8051.

- -> Main functional Blocks in 8051 micro controlle are

- · CPU

- . ROM

- . RAM

- · Hoports

- · System Timing Control unit

- Timeres

- · Interrupt Sources.

0

# -> CPU contains

- Antimetic and logical wit is used for the

- A: Accumulator is a 8-bit register, which is used for Asimeratic operations.

- D. . Reporter's in at 8-bit rejected in used in only two instructions MULA; B and DIVA; B.

- PC: Program Counter in a 16-bit register, points.

to be address of next Instruction to be executed

from Rom.

- DPTR: Dera pointer is a 16-bit register, it is divided into two parts DPH & DPL. DPH for Higher order 8-bits, DPL for lower order 8-bits.

- micro controller. wed to Store programs.

Addron range of memory (Rom) 85.

address. 0000 1111 1111 (OFFFH)

Standing 0000 0000 0000 0000 (0000H)

Tradicate The Arithmetic condition of Accumulator.

Flag register in Bori in Called as program Status Word (PSW).

This Special function register PSW is also bit addressable.

| h      | nc     | 2010 | PSWOY | E-1005d | PSW0.2 | PSWO.1 | pswo.o |

|--------|--------|------|-------|---------|--------|--------|--------|

| 1500.4 | L2M0.0 | E0 - | RSI,  | RSD     | OV     | -      | P      |

| CY     | THC.   |      |       |         |        |        | _      |

- -> In Size active flags, four are states flags, two one Register Bank Scient flags

- -> Status Plays parily (P), overflow (OV), Auxillary Corry(AL)

and Carry (CP) are reflect the Reg Result of the ALU.

porcity (1): If result contain even no. of i's, parcity is the

overfine (OV): In Signed operations, if magnetude bit provides earry, overflow sets set.

Auxillery Carry: If my carry form & Lower missle to Higher nisble to Higher nisble to Higher to Higher nisble to Higher to Higher nisble to Higher to Higher

Courry (e4): If There is Any Carry From nost Cyneficant bit, carry flag gots set.

Er: Add 54.4 to 444. rescut Will reflect flows as Shown below :

rocoult: parity: P=0; (odd no.) ones)

A.C =0; (no Carry from PstoD4)

OV =0; (It is not a signed opelable)

'(4 =0; (there is no Carry).

-> Registed prant School Bits, in when to select the register Bank

| PCI | 010 | BULL BANK      |

|-----|-----|----------------|

| 0   | 0   | Registee MANKO |

| 0   | (   | legiste enurs  |

| 1   | 0   | Register BANK) |

| t   | 1   | legion bank 3. |

Tritially by default always carb'o' is selected.

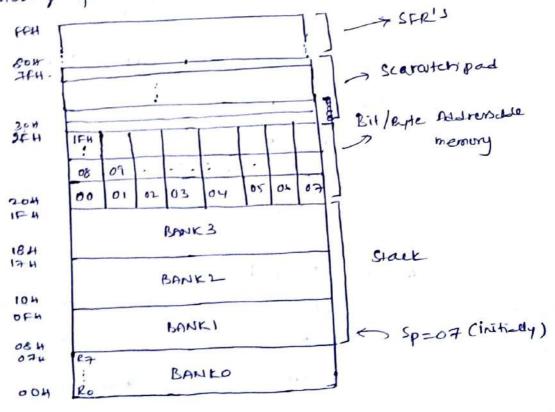

- -> Stouwere of lam (00 805) legitu Bank and Stack;

- . 128 begins of RAM in assistable in RAM, apart from their another 128 begins one assorbed for special function regulated.

- PAM, Extra 128 Bytes RAM Which is 80H to FFH which for Storage of SFR (Special function registrons).

-fig. Structure of RAM

- There are tour registed banks, in each register bank.

There are the eight 8-bit registers available from for RT.

- → By default Bank'O' in Scheded, For Bank O, RD has address OTH.

- -> Ro to Rz are byte addressable.

- -> Locations doll to 2FH in bit addressable RAM means each bit from both to FFH in This we can ser in reset.

- -> hocetions 30th to 1FH is used as Scratch pad means, we can use this space for data standing and writing (as)

for data storage.

- -> RAM locations from 08# to 1F# Can be used as Start.

Stack is well to Store the data remporarily.

Stack is Last in First out (LIFO).

- -> Stack pointer in a 8-bit reprotect. It Indicates but

consent RAM address at available for stack ton it

points the top of stack.

- Intially by defeut -+ 07 H become first locationy.

Stack in 08 H.

- # Special function registers (SFR'S) :-

- A Exter D8 bytes RAM which is used to store the EFE's, one used to Interrupt Control, timen/country, when, are used to Interrupt Control, timen/country, when, proceed through regrerors between proce Control outer performed Through regrerors between 80H to FFH.

For removing this situation we use the stack from location 30H to 7FH by shifting SP to 2FH. MOV SP,#2FH;

#### DPTR → Data Pointer in 8051

- 16 bit register, it is divided into two parts DPH and DPL.

- DPH for Higher order 8 bits, DPL for lower order 8 bits.

- DPTR, DPH, DPL these all are SFRs in 8051.

#### Special Function Register

- (See Fig.) RAM scratch pad, there is extra 128 byte RAM which is used to store the SFRs

- Following figure shows special function bit address, all access to the four I/O ports CPU register, interrupt control register, timer/counter, UART, power control are performed through registers between 80H and FFH.

#### Byte Addressable SFR with byte address

SP - Stack printer - 81H

DPTR - Data pointer 2 bytes

DPL - Low byte - 82H

DPH - High byte - 83H

TMOD - Timer mode control - 89H

TH9 - Timer 0 Higher order bytes - 8CH

TLO - Timer 0 Low order bytes - 8AH

THI – Timer 1 High bytes = 80H

TL1 - Timer 1 Low order byte = 86H

SBUF - Serial data buffer = 99H

PCON - Power control - 87H.

#### Instruction set of 8051

The 8051 instructions are divided among five functional groups:

- 1. Arithmetic

- 2. Logical

- 3. Data transfer

- 4. Boolean variable

- 5. Program branching

#### 1. Arithmetic Instructions:

#### **ADD** A, source A = A +source

- > The instruction ADD is used to add two operands

- > Destination operand is always in register A Source operand can be a register, immediate data, or in memory

Ex: MOV A,#0F5H

ADD A, #0BH

#### DA A; decimal adjust for addition

- The DA instruction is provided to correct the aforementioned problem associated with BCD addition

- The DA instruction will add 6 to the lower nibble or higher nibble if need

Ex:

MOV A,#47H; A=47H first BCD operand

MOV B,#25H; B=25H second BCD operand

ADD A,B; hex(binary) addition(A=6CH)

DA A; adjust for BCD addition (A=72H)

#### After an ADD or ADDC instruction

- If the lower nibble (4 bits) is greater than 9, or if AC=1, add 0110 to the lower

- If the upper nibble is greater than 9, or if CY=1, add 0110 to the upper 4 bits

SUBB A, source ; A = A - source - CY

- To make SUB out of SUBB, we have to make CY=0 prior to the execution of the instruction

- Notice that we use the CY flag for the borrow

# MUL AB; AxB, 16-bit result in B, A

- The 8051 supports byte by byte multiplication only

- The byte are assumed to be unsigned data

Ex:

MOV A,#25H;

load 25H to reg. A

MOV B,#65H;

load 65H to reg. B

MUL AB;

25H \* 65H = E99

where; B = OEH and A = 99H

#### DIV AB;

divide A by B, A/B

- The 8051 supports byte over byte division only

- The byte are assumed to be unsigned data

Ex:

MOV A,#95;

load 95 to reg. A

MOV B,#10;

load 10 to reg. B

MUL AB;

A = 09(quotient) and; B = 05(remainder)

2. Logical Instructions:

#### ANL destination, source ;dest = dest AND source

- This instruction will perform a logic AND on the two operands and place the result in the destination

- The destination is normally the accumulator

- The source operand can be a register, in memory, or immediate

Ex:

MOV A,#35H;

A = 35H

ANL A,#0FH;

A = A AND 0FH

# ORL destination, source ; dest = dest OR source

- The destination and source operands are ORed and the result is placed in the destination

- The destination is normally the accumulator

- > The source operand can be a register, in memory, or immediate

Ex:

MOV A,#04H;

A = 04

ORL A,#68H;

A = 6C

#### XRL destination, source ; dest = dest XOR source

- This instruction will perform XOR operation on the two operands and place the result in the destination

- The destination is normally the accumulator

- > The source operand can be a register, in memory, or immediate

Ex:

MOV A,#54H

XRL A,#78H

#### CPL A; complements the register A

- This is called 1's complement

- To get the 2's complement, all we have to do is to to add 1 to the 1's complement Ex:

MOV A, #55H

CPL A; now A=AAH; 0101 0101(55H); becomes 1010 1010(AAH)

CJNE destination, source, rel. addr.

- The actions of comparing and jumping are combined into a single instruction called CJNE (compare and jump if not equal)

- The CJNE instruction compares two operands, and jumps if they are not equal

- The destination operand can be in the accumulator or in one of the Rn registers

- > The source operand can be in a register, in memory, or immediate

- > The operands themselves remain unchanged

- It changes the CY flag to indicate if the destination operand is larger or smaller

#### **Rotation Instructions:**

## RR A ;rotate right A

- > In rotate right

- > The 8 bits of the accumulator are rotated right one bit, and

- > Bit D0 exits from the LSB and enters into MSB, D7

## RL A ;rotate left A

- In rotate left

- > The 8 bits of the accumulator are rotated left one bit, and

- > Bit D7 exits from the MSB and enters into LSB, D0

#### RRC A ;rotate right through carry

- In RRC A

- > Bits are rotated from left to right

- > They exit the LSB to the carry flag, and the carry flag enters the MSB

## RLC A ;rotate left through carry

- ➤ In RLC A

- > Bits are shifted from right to left

- > They exit the MSB and enter the carry flag, and the carry flag enters the LSB

#### 3. Data Transfer Instructions:

#### MOV A, R2; moving data from source R2 to destination Accumulator

- > This instruction will perform a Move the data in source to the destination.

- > The destination is normally the register, memory location.

- > The source operand can be a register, in memory, or immediate

#### 4. Boolean Instructions:

There are several instructions by which the CY flag can be manipulated directly

Instruction Function

SETB C

CLR C

CPL C

Make CY = 1

Clear carry bit (CY = 0)

Complement carry bit

MOV b,C Copy carry status to bit location (CY = b)

MOV C,b Copy bit location status to carry (b = CY)

JNC

JC

ANL C,bit

ANL C,bit

AND CY with bit and save it on CY

AND CY with inverted bit and save it on CY

ORL C,bit OR CY with bit and save it on CY

ORL C,/bit OR CY with inverted bit and save it on CY

# 5. Program Branching Instructions

DJNZ reg, Label

- > Repeating a sequence of instructions a certain number of times is called a loop

- > The register is decremented

- > If it is not zero, it jumps to the target address referred to by the label

- > Prior to the start of loop the register is loaded with the counter for the number of repetitions

- ➤ Counter can be R0 R7 or RAM location

Jump only if a certain condition is met

JZ label

;jump if A=0

JNC label

;jump if no carry, CY=0

- > If CY = 0, the CPU starts to fetch and execute instruction from the address of the label

- > If CY = 1, it will not jump but will execute the next instruction below JNC

JBC Jump if bit = 1 and clear bit

JNB Jump if bit = 0

JB Jump if bit = 1

JNC Jump if CY = 0

JC Jump if CY = 1

CJNE reg,#data Jump if byte  $\neq$  #data

CJNE A,byte Jump if A  $\neq$  byte

DJNZ Decrement and Jump if  $A \neq 0$

JNZ Jump if  $A \neq 0$ JZ Jump if A = 0

#### Addressing Modes of 8051

In short, a way to addressing a operand is nothing but addressing mode. Operand means data on which we are going to operate i.e source data. We can address the operand using direct address or by using register or we can address the data using some numerical value etc.

#### MOVA,#6BH

In this example 6BH is operand i.e. source data. After execution of this instruction 6BH is added to the accumulator.

We can execute this instruction by using 5 different ways i.e we can use 5 different addressing modes to execute this instruction. Following are the different type of addressing modes.

- Immediate addressing mode

- · Direct addressing mode

- · Register addressing mode

- Register indirect addressing mode

- Indexed addressing mode.

#### 1. Immediate addressing mode:

As word indicates 'immediate' this addressing mode transfers 8 bit immediate data to destination.

MOVA,#6BH

This instruction moves immediate data hex 6B to accumulator.

#### 2. Direct addressing mode:

This is type of addressing mode in which the address of the data (source data) is given as operand..i.e. it is given directly in the form of numerical data.

MOVB,20H

The instruction above moves value at address 20H memory location to register B.

Here 20H is address of SFR.

The difference between direct addressing and immediate addressing mode is, we don't use '#' in direct addressing mode, unlike immediate mode.

#### 3. Register addressing mode:

This is type of addressing mode in which we use the register name directly as source data.

MOV A, R5

After execution of this instruction content of register R5 is get copied to location accumulator.

#### 4. Register direct addressing mode:

In this mode of addressing address of source data is given by value at register indirectly that's why we call it as a indirect register addressing mode.

Here in this instruction register R1 holds the address, suppose value at R1 is '20H' then after execution of above instruction value at location 20H is transferred to to accumulator. Here symbol '@' indicates address. In this type addressing mode we can use only register R0 and R1 to provide indirect address.

#### 5. Indexed addressing mode:

In this type of addressing mode we use following instruction:

1. MOVC A, @A+DPTR and 2. MOVC A, @A+PC

'MOVC A, @A+DPTR' instruction copies value at the location given by result of addition of content of accumulator and 16 bit register DPTR. Suppose Accumulator contain '01H' and DPTR contains value '1000H' then after the execution of instruction 'MOVC A, @A+DPTR the value at address '1001H' will be transferred to accumulator.

'MOVC A, @A+PC' instruction copies value at the location given by result of addition of content of accumulator and 16 bit register PC (Program counter). Suppose Accumulator contain '01H' and PC contains value '1000H' then after the execution of instruction 'MOVC A, @A+DPTR the value at address '1001H' will be transferred to accumulator.

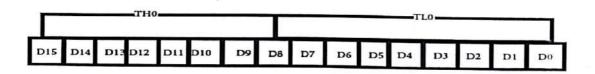

#### Timer Operation in 8051 Micro controller

- The 8051 has two counters/timers which can be used either as timer to generate a time delay or as counter to count events happening outside the microcontroller.

- > The 8051 has two timers: timer0 and timer1. They can be used either as timers or as counters. Both timers are 16 bits wide. Since the 8051 has an 8-bit architecture, each 16-bit is accessed as two separate registers of low byte and high byte. First we shall discuss about Timer0 registers.

- > Timer0 registers is a 16 bits register and accessed as low byte and high byte. The low byte is referred as a TL0 and the high byte is referred as TH0. These registers can be accessed like any other registers.

Fig. Timero

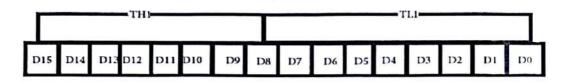

Timer1 registers is also a 16 bits register and is split into two bytes, referred to as TL1 and TH1.

Fig. Timer1

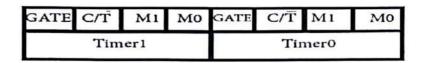

#### TMOD (timer mode) Register:

- > This is an 8-bit register which is used by both timers 0 and 1 to set the various timer modes.

- In this TMOD register, lower 4 bits are set aside for timer0 and the upper 4 bits are set aside for timer1.

- > In each case, the lower 2 bits are used to set the timer mode and upper 2 bits to specify the operation.

Fig. TMOD Register

- > The hardware way of starting and stopping the timer by an external source is achieved by making GATE=1 in the TMOD register. And if we change to GATE=0 then we do not need external hardware to start and stop the timers.

- > The second bit is C/T bit and is used to decide whether a timer is used as a time delay generator or an event counter. If this bit is 0 then it is used as a timer and if it is 1 then it is used as a counter.

- > In upper or lower 4 bits, the last bits third and fourth are known as M1 and M0 respectively. These are used to select the timer mode.

| M0    | M1    | Mode Operating Mode |                                                                      |

|-------|-------|---------------------|----------------------------------------------------------------------|

| 0     | 0     | 0                   | 13-bit timer mode, 8-bit timer/counter THx and TLx as 5- bit         |

| presc | alar. |                     |                                                                      |

| 0     | 1     | 1 16                | bit timer mode, 16-bit timer/counters THx and TLx are cascaded;      |

|       |       |                     | are no prescalar.                                                    |

| 1     | 0     | 2 8                 | 8-bit auto reload mode, 8-bit auto reload timer/counter; THx holds a |

|       |       | Valu                | e which is to be reloaded into TLx each time it overflows.           |

| 1     | 1     | 3 S                 | pilt timer mode                                                      |

#### Mode 1

- It is a 16-bit timer; therefore it allows values from 0000 to FFFFH to be loaded into the timer's registers TL and TH.

- > After TH and TL are loaded with a 16-bit initial value, the timer must be started. We can do it by "SETB TR0" for timer 0 and "SETB TR1" for timer 1.

- After the timer is started.

- It starts count up until it reaches its limit of FFFFH. When it rolls over from FFFF to 0000H, it sets high a flag bit called TF (timer flag).

- > This timer flag can be monitored. When this timer flag is raised, one option would be stop the timer with the instructions "CLR TR0" or CLR TR1 for timer 0 and timer 1 respectively.

- Again, it must be noted that each timer flag TF0 for timer 0 and TF1 for timer1. After the timer reaches its limit and rolls over, in order to repeat the process the registers TH and TL must be reloaded with the original value and TF must be reset to 0.

#### Example program

To create a square wave of 50% duty cycle (with equal portions high and low) on the P1.5 bit. Timer 0 is used to generate the time delay

MOV TMOD,#01

HERE: MOV TL0,#0F2H

MOV TH0,#0FFH

CPL P1.5

ACALL DELAY

SJMP HERE

SJMP HERE

MOV TMOD,#01

;Timer 0, mode 1(16-bit mode)

;TL0=F2H, the low byte

;TH0=FFH, the high byte

;toggle P1.5

In the above program notice the following step.

1. TMOD is loaded.

2. FFF2H is loaded into TH0-TL0.

3. P1.5 is toggled for the high and low portions of the pulse.

#### DELAY:

SETB TR0 ;start the timer 0

AGAIN: JNB TF0, AGAIN ;monitor timer flag 0;until it rolls over

CLR TR0 ;stop timer 0

CLR TF0 ;clear timer 0 flag

RET

4. The DELAY subroutine using the timer is called.

5. In the DELAY subroutine, timer 0 is started by the SETB TR0 instruction.

6. Timer 0 counts up with the passing of each clock, which is provided by the crystal oscillator. As the timer counts up, it goes through the states of FFF3,FFF4, FFF5, FFF6, FFF7, FFF8, FFF9, FFFA, FFFB, and so on until it reaches FFFFH. One more clock rolls it to 0, raising the timer flag (TF0=1). At that point, the JNB instruction falls through.

7. Timer 0 is stopped by the instruction CLR TR0. The DELAY subroutine ends and the process is repeated.

#### Mode 2

- It is an 8 bit timer that allows only values of 00 to FFH to be loaded into the timer's register TH.

- After TH is loaded with 8 bit value, the 8051 gives a copy of it to TL. Then the timer must be started. It is done by the instruction "SETB TR0" for timer 0 and "SETB TR1" for timer 1. This is like mode 1.

- > After timer is started, it starts to count up by incrementing the TL registers. It counts up until it reaches its limit of FFH. When it rolls over from FFH to 00.

- > It sets high the TF (timer flag). If we are using timer 0, TF0 goes high; if using TF1 then TF1 is raised.

- When TI register rolls from FFH to 00 and TF is set to 1, TL is reloaded automatically with the original value kept by the TH register. To repeat the process, we must simply clear TF and let it go without any need by the programmer to reload the original value. This makes mode 2 auto reload, in contrast in mode 1 in which programmer has to reload TH and TL.

## Example Program

> To find the frequency of the square wave generated on pin P1.0 in the following program

MOV TMOD,#20H

MOV TH1,#5

SETB TR1

BACK: JNB TF1,BACK

CPL P1.0

CLR TF1

SJMP BACK

SJMP BACK

(T1/8-bit/auto reload

;T11 = 5

; start the timer 1

;till timer rolls over

;P1.0 to hi, lo

;clear Timer 1 flag

;mode 2 is auto-reload

## Solution:

First notice the target address of SJMP. In mode 2 we do not need to reload TH since it is autoreload. Now (256 - 05) × 1.085 us = 251 × 1.085 us = 272.33 us is the high portion of the pulse. Since it is a 50% duty cycle square wave, the period T is twice that; as a result T = 2 × 272.33 us = 544.67 us and the frequency =1.83597 kHz

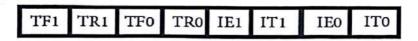

#### TCON register

TCON register is the timer control special function register. In which lower nibble is used to control interrupt operation and higher nibble is used to control timer operation. Bits and symbol and functions of every bits of TCON are as follows:

Fig. TCON Register

| BIT | Symbol | Functions                                                                                                                                                                                                                                     |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TFI    | Timer1 over flow flag. Set when timer rolls from all 1s to 0. Cleared When the processor vectors to execute interrupt service routine Located at program address 001Bh.                                                                       |

| 6   | TR1    | Timer 1 run control bit. Set to 1 by programmer to enable timer to count;<br>Cleared to 0 by program to halt timer.                                                                                                                           |

| 5   | TF0    | Timer 0 over flow flag. Same as TF1.                                                                                                                                                                                                          |

| 4   | TR0    | Timer 0 run control bit. Same as TR1.                                                                                                                                                                                                         |

| 3   | IE1    | External interrupt 1 Edge flag. Not related to timer operations.                                                                                                                                                                              |

| 2   | IT1    | External interrupt 1 signal type control bit. Set to 1 by program to Enable external interrupt 1 to be triggered by a falling edge signal. Set To 0 by program to enable a low level signal on external interrupt 1 to generate an interrupt. |